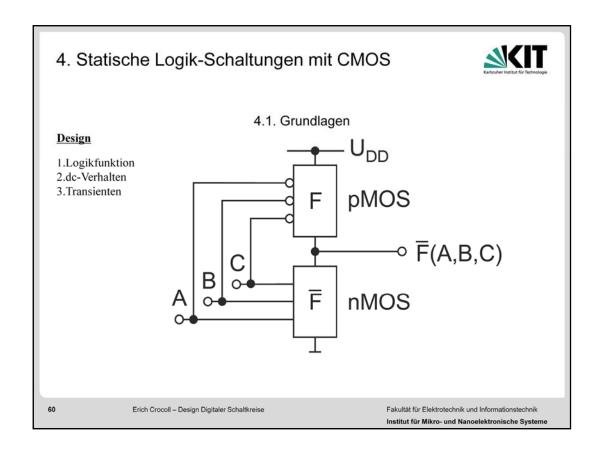

Logische Funktionen in CMOS Technologie lassen sich vereinfacht durch einen nMOSund einen pMOS-Block darstellen.

Die Art der Verschaltung der Transistoren (Reihenschaltung – Parallelschaltung) ergibt dann die gewünschte logische Funktion.

Als nächstes wollen wir uns die "kritischen" Pfade näher betrachten.

Da wir ja in CMOS-Schaltungen immer Kapazitäten umladen müssen sind die Reihenschaltungen der Transistoren die entscheidenden Elemente.

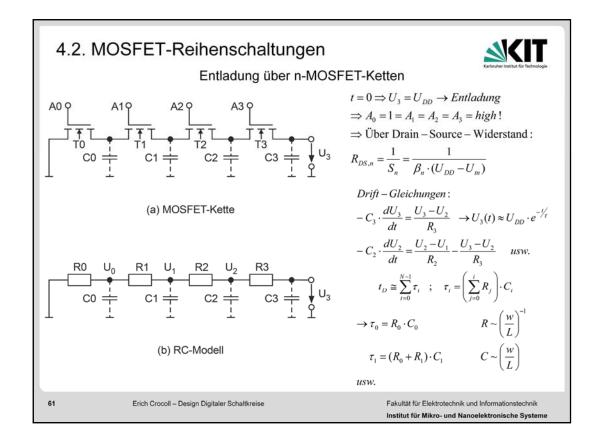

Zunächst wird die Reihenschaltung von nMOS-Transistoren analysiert. Dazu kann eine Schaltung nach obigem Bild skizziert werden.

Über die nMOS-Ketten wird die Ausgangskapazität des Gatters entladen. Ausgehend von einem High-Pegel am Ausgang (U<sub>3</sub>) wird durch das Einschalten aller Transistoren (TO ...

T3) die in  $C_3$  gespeicherte Ladung über die Drain-Source Widerstände der 4 Transistoren nach Masse abgeleitet. In den intrinsischen Kapazitäten der Transistoren ist ebenfalls Ladung gespeichert, was durch C0 .. C2 angedeutet ist.

Der Drain-Source Widerstand der Transistoren ist wie angegeben definiert.

Damit lässt sich ein RC-Ersatzschaltbild erstellen und die Entladung des Ausgangs vereinfacht formelmäßig darstellen.

Wir können die Verzögerungszeit  $\tau_D$  als Summe der einzelnen Entladezeitkonstanten  $\tau_i$  definieren.

Die Zeitkonstanten  $\tau_i$  können nach den angegebenen Formeln bestimmt werden. Anmerkung: Nur  $C_3$  ist auf  $U_{DD}$  aufgeladen. Die Kapazitäten C0, C1 und C2 können nur auf max.  $U_{DD}$ - $n\cdot U_{th}$  aufgeladen werden. Substrateffekte werden vernachlässigt.

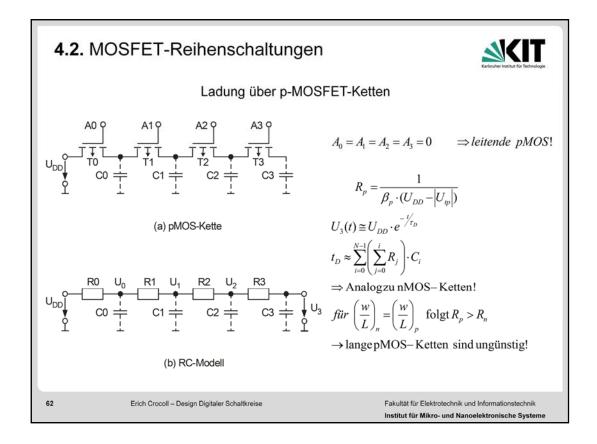

Für das Aufladen der Ausgangskapazität über pMOS-Ketten gelten die gleichen Ansätze, die wir für die nMOS-Ketten angenommen haben.

Wir erhalten damit formelmäßig auch die gleichen Ergebnisse.

Die Verzögerungszeit  $\tau_D$  ist nicht in beiden Fällen gleich groß, auch wenn  $\beta_n = \beta_p$  ist, da die intrinsischen Transistorkapazitäten aufgrund der in diesem Fall 3-fach größeren Fläche der pMOS Transistoren größer sind, als die der nMOS Transistoren.

Wird aber auch noch auf Chipfläche optimiert, d.h. die Weite der PMOS-Tr. ist weniger groß, verschlechtert sich der Aufladevorgang.

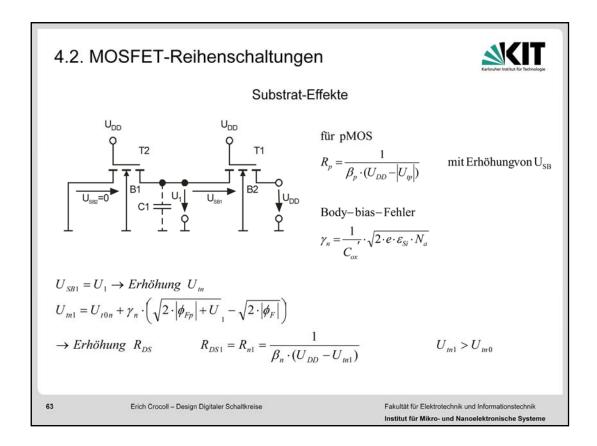

Ziehen wir nun noch die Substrateffekte hinzu, die sich ergeben, wenn die Transistorketten in einer gemeinsamen Wanne integriert sind, müssen wir die Drain-Source Widerstände der Ketten entsprechend des gezeigten Beispiels korrigieren.

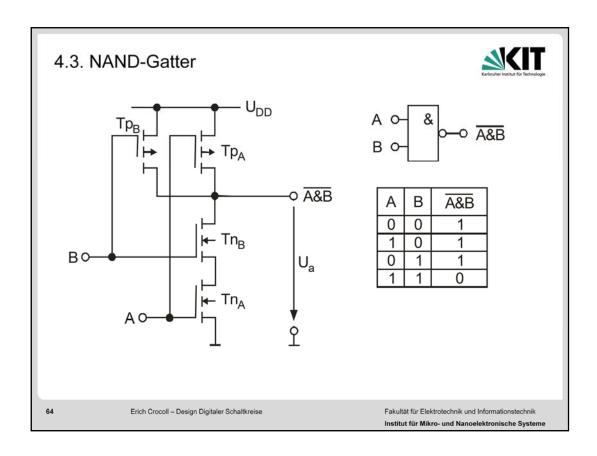

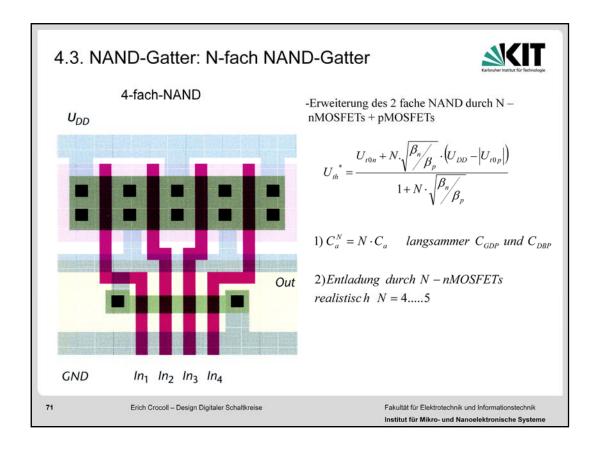

Nach den Betrachtungen der Umladezeitkonstanten wollen wir und jetzt mit den statischen und dynamischen Eigenschaften einfacher logischer Gatter befassen. Ein NAND-Gatter mit zwei Eingängen besteht aus 2 in Reihe geschalteter nMOS- und 2 parallel geschalteter pMOS-Transistoren.

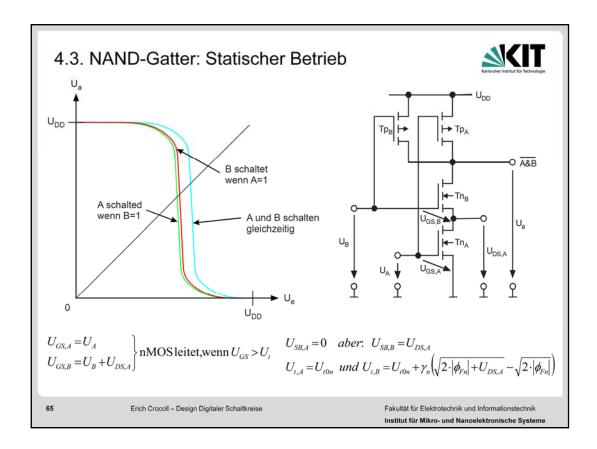

Im statischen Betrieb betrachten wir wieder die Übertragungsfunktion. Dabei stelle wir fest, dass im Gegensatz zum Inverter nun 3 unterschiedliche Übertragungskennlinien vorhanden sind.

Die unterschiedlichen Schaltpunkte ergeben sich aus den 3 Varianten, welches Eingangssignal das Umschalten des Ausgangs von H -> L bewirkt.

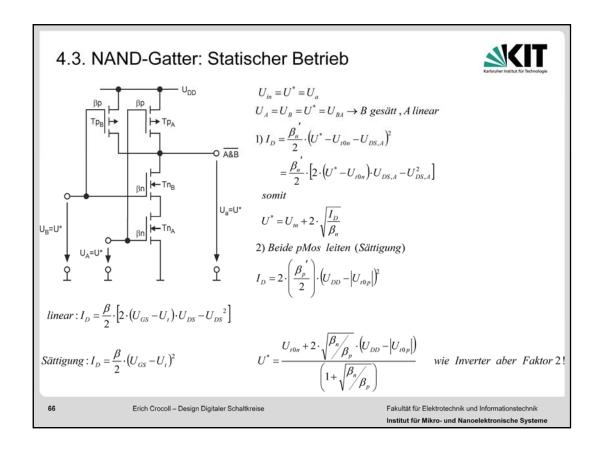

Aus den Maschengleichungen für die Eingangsspannungen an A bzw. B können die Spannungen bestimmt werden, bei denen die Transistoren A bzw. B beginnen zu leiten. Liegt ein gemeinsames Signal an A und B an, haben wir einen Inverter. Aus dem Inverterverhältnis  $\beta$  kann der zugehörige Schaltpunkt berechnet werden.

Die Berechnungen für diesen Schaltpunkt sind hier ausgeführt.

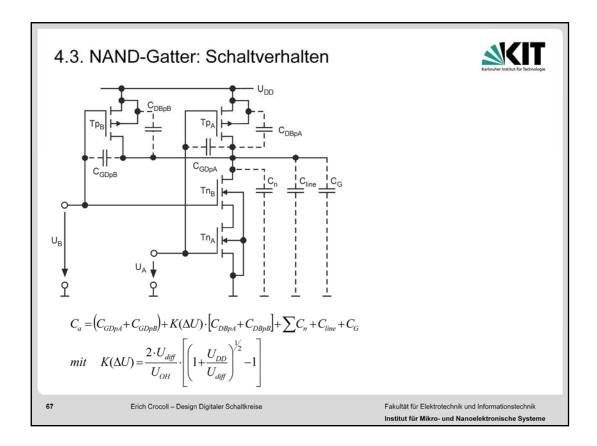

Als nächstes wollen wir das Schaltverhalten eines NAND-Gatters untersuchen. Dazu müssen zuerst alle Kapazitäten, die auf den Ausgang wirken, erfasst werden. Dies sind zum einen die intrinsischen Kapazitäten der Transistoren selbst und die am Ausgang der Schaltung wirksamen Lastkapazitäten der Verbindungsleitung zum nächsten Gatter und die Eingangskapazität des angesteuerten Gatters selbst. Wir erhalten damit die angegebene Formel für C<sub>a</sub>.

#### 4.3. NAND-Gatter: LH-Schaltzeit (Laden)

$$U_a(t=0) = 0$$

;  $(A = B = 1)$

Laden durch pMOS

$$t_{LH} = \tau_{p} \cdot \left[ \frac{2(|U_{1p}| - U_{0})}{(|U_{DD}| - |U_{1p}|)} + \ln \left( \frac{2 \cdot (|U_{DD}| - |U_{1p}|)}{|U_{0}|} - 1 \right) \right]$$

$$U_0 = 0.1 \cdot U_{DD}$$

$\rightarrow 10\% U_{DD}$

$$U_{0} = 0,1 \cdot U_{DD} \longrightarrow 10\% \ U_{DD}$$

$$\tau_{p} = \frac{C_{a}}{\left(\sum_{j} \beta_{pj}\right) \cdot \left(U_{DD} - \left|U_{pp}\right|\right)} \qquad \text{für } \left(\sum_{j} \beta_{j}\right) \ \text{gilt:}$$

$$A = 0 \rightarrow \beta_{p1} \quad \text{(Einst$$

$$A = 0 \rightarrow \beta_{p1}$$

(Eingang A bewirkt Umschalten)

$B = 0 \rightarrow \beta_{p2}$  (Eingang B bewirkt Umschalten)

$$A = B = 0$$

(beide Eingänge bewirken Umschalten)

$$\left(\sum_{j} \beta_{j}\right) = \left(\beta_{p1} + \beta_{p2}\right)$$

68 Erich Crocoll - Design Digitaler Schaltkreise Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische Syst

Zuerst wird der Aufladevorgang am Ausgang ( $t_{LH}$ ) betrachtet.

Die Anstiegs- und Abfallzeiten sind bekanntlich durch die Ausgangspegel 10%-90% definiert.

Wenn wir die Gleichungen , die wir beim Inverter abgeleitet haben leicht modifiziert anwenden, erhalten wir die hier angeführten Ergebnisse. Wir erkennen, dass in der Foemel für die Zeitkonstante  $\tau_{\text{p}}$  im Nenner die Größe  $\beta_{\text{p}}$  durch eine Summe ersetzt wurde.

Abhängig vom für das Umschalten wirksamen Eingang setzen wir dann die entsprechenden Werte ein.

Man erkennt, dass im Falle des "Inverterbetriebs" die Zeitkonstante aufgrund der Parallelschaltung der Transistoren nur noch halb so groß ist.

### 4.3. NAND-Gatter: HL-Schaltzeit (Entladen)

$$U_a(t=0) = U_{DD}$$

$$t_{D} \cong R_{nA} \cdot C_{nA} + (R_{nA} + R_{nB}) \cdot C_{a}$$

$$t_{HL} = \tau_{n} \cdot \left[ \frac{2 \cdot (U_{m} - U_{0})}{U_{DD} - U_{m}} + \ln \left( \frac{2 \cdot (U_{DD} - U_{m})}{U_{0}} - 1 \right) \right]$$

$$\tau_{n} \cong \frac{C_{a}}{C_{a}}$$

$$\tau_{n} \cong \frac{C_{a}}{\beta_{n,eff} \cdot \left(U_{DD} - U_{tn}\right)}$$

$$\beta_{n,eff} = \beta_n' \cdot \left[ \frac{W}{\left( L_{nA} + L_{nB} \right)} \right]$$

wie Einzel – MOSFET mit  $L_{nA} + L_{nB}$

Erich Crocoll - Design Digitaler Schaltkreise 69

Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische Syste

Beim Umschaltvorgang von H nach L am Ausgang können wir die gleichen Überlegungen anstellen.

Wir gehen wieder von den Gleichungen des Inverters aus und ersetzen wider bei der Zeitkonstante das  $\beta_n$  durch  $\beta_{n,eff}$ .

In diesem Fall sind die beiden nMOS-Transistoren immer in Reihe geschaltet. Damit wird  $\beta_{\text{n,eff}}$  durch die angeführte GI. beschrieben.

Abhängig davon, welcher Transistor das Umschalten auslöst, muss die korrekte Schwellspannung in die Gleichung für  $t_{HL}$  eingesetzt werden.

#### 4.3. NAND-Gatter: Design

1. Timing

$\beta_n, \beta_p$  – Anschließend erst dc

$$LH \to pMOS \ \left(\frac{W}{L}\right)_{p1} und \left(\frac{W}{L}\right)_{p2}$$

wenn ein MOSFET leitet:

$$\left(\frac{W}{L}\right)_{p} = \frac{C_{a}}{\beta_{n}' \cdot \tau_{p} \left(U_{DD} - \left|U_{pp}\right|\right)}$$

$$HL \to nMOS \to identisch \left(\frac{W}{L}\right)_{n}$$

$$\left(\frac{W}{L}\right)_{n} = \frac{2 \cdot C_{a}}{\beta_{n}' \cdot \tau_{n}(U_{DD} - U_{m})}$$

$$\left(\frac{W}{L}\right)_{n} = \frac{2 \cdot C_{a}}{\beta_{n}' \cdot \tau_{n} (U_{DD} - U_{m})}$$

$$2.DC - S^*$$

Schaltpunkt  $\rightarrow \frac{\beta_n}{\beta_p}$  Bestimmung

70

Erich Crocoll - Design Digitaler Schaltkreise

Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische Syst

Aus den bisherigen Analysen des NAND-Gatters ergeben sich nun für das Schaltungsdesign folgende Schritte:

- 1. Auswahl der Schaltzeiten über die Bestimmung der W/L-Verhältnisse der Transistoren

- Dazu werden die Formeln für die Zeitkonstanten entsprechend umgeformt

- 2. Aus den ermittelten Werten können nun die Schaltpunkte bestimmt werden.

Gegebenenfalls müssen zur Optimierung der Zelle Iterationsschritte durchgeführt werden.

Ist dies geschehen, kann das Layout der Zelle in Angriff genommen werden.

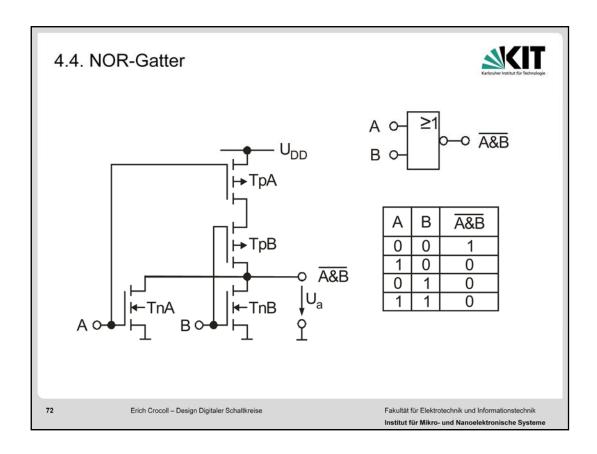

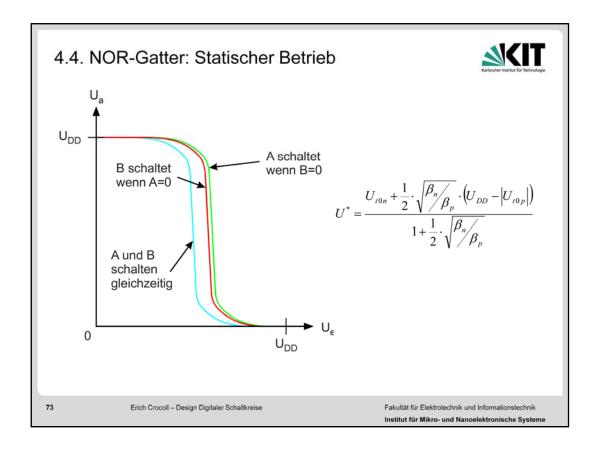

Für das NOR-Gatter erfolgt nun eine Analyse in der gleichen Weise wie zuvor beim NAND-Gatter.

Auch hier sind die Übertragungskennlinien abhängig davon, welcher der beiden Eingänge den Umschaltvorgang auslöst.

Für den Schaltpunkt ergibt sich die gezeigte Formel.

Vergleichen wir diese mit der des NAND-Gatters erkennen wir, dass anstelle des Faktors 2 nun ein Faktor ½ in der Gleichung auftritt.

Diese Änderung wird durch die hier "vertauschte Reihen- bzw. Parallelschaltung der nund p-Kanal Transistoren verursacht.

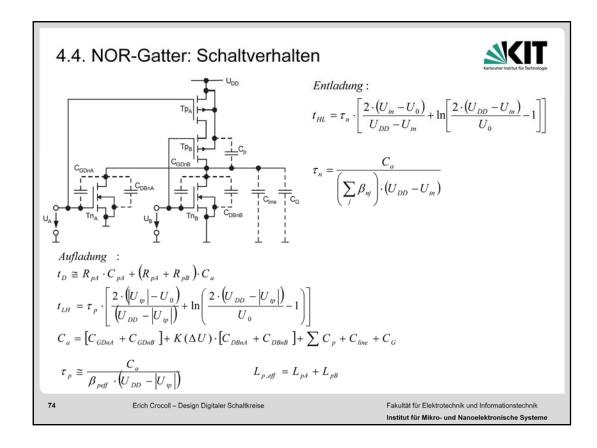

Für die Analyse des Schaltverhaltens wenden wir auch hier die Grundlagen vom Inverter an.

Wir erkennen, dass analog zu den bisherigen Betrachtungen auch hier die Gleichungen zur Bestimmung der der Schaltzeiten "vertauscht" sind.

## 4.4. NOR-Gatter: Design and n-fach-Gatter

1. Schaltverhalten → Aspecktverhältnis

$$\begin{aligned} & High-Low: \left(\frac{w}{L}\right)_{n} = \frac{C_{a}}{\beta_{n}' \cdot \tau_{p} \cdot (U_{DD} - U_{in})} \\ & L \rightarrow H: \left(\frac{w}{L}\right)_{p} = \frac{2 \cdot C_{a}}{\beta_{n}' \cdot \tau_{p} \left(U_{DD} - \left|U_{ip}\right|\right)} \\ & 2. \ Setzen \ von \ U^{*} \rightarrow Optimierung \ von \left(\frac{\beta_{n}}{\beta_{p}}\right) \end{aligned}$$

$$L \to H : \left(\frac{w}{L}\right)_p = \frac{2 \cdot C_a}{\beta_n' \cdot \tau_n \left(U_{DD} - |U_m|\right)}$$

$n-fach\ NOR$ :

$$U^* = \frac{U_{t0n} + \left(\frac{1}{N}\right) \cdot \sqrt{\frac{\beta_n}{\beta_p}} \cdot \left(U_{DD} - \left|U_{t0p}\right|\right)}{1 + \left(\frac{1}{N}\right) \cdot \sqrt{\frac{\beta_n}{\beta_p}}} \qquad N_{\text{max}} = 4.....5$$

Erich Crocoll - Design Digitaler Schaltkreise

Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische Syste

Auch für das Design dieser Zelle gelten die gleichen Vorgehensweisen wie beim NAND-Gatter.

# 4.5. Vergleich zwischen NAND- und NOR-Gatter

NAND und NOR =CMOS- Design

- Bei gleichen N und gleicher Fläche sind NAND schneller!

Why?

Serienschaltung der Transistoren begrenzt die Umschaltzeit!

$$ightarrow NAND - H

ightarrow L \, \ddot{u}ber \, n - MOSFET - Kette \

ightarrow NOR

ightarrow L

ightarrow H \, \ddot{u}ber \, p - MOSFET - Kette \ da \, R_n < R_p \ au_{D,NAND} < au_{D,NOR}$$

76

Erich Crocoll – Design Digitaler Schaltkreise

Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische Systeme

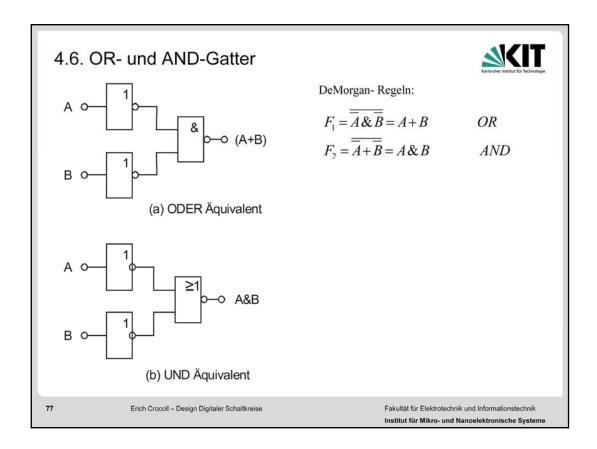

Um OR bzw. AND-Gatter aufzubauen gibt es 2 Möglichkeiten:

- 1. Das Nachschalten eines Inverters an das NOR bzw. NAND-Gatter,

- 2. das Vorschalten von Invertern und ein "Vertauschen" der Logikfunktion, wie dies auf dieser Folie gezeigt wird.

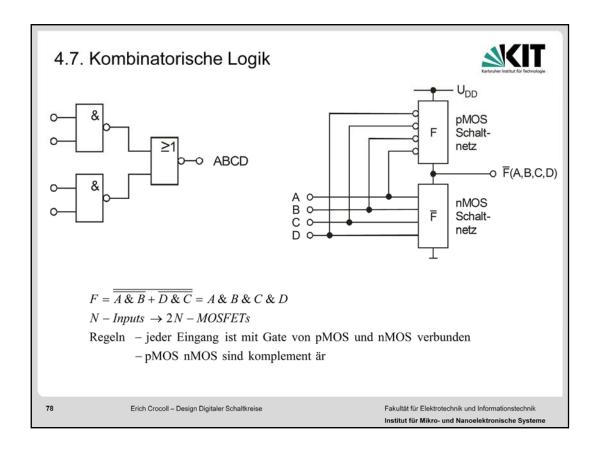

Diese Art des Aufbaus von Logikschaltkreisen wir auch als kombinatorische Logik bezeichnet.

Für eine allgemeine Betrachtung geht man wieder davon aus, dass man schaltnetze aus nMOS und pMOS verwendet und jeder Eingang der Schaltung immer ein komplementäres Transistorpaar ansteuert.

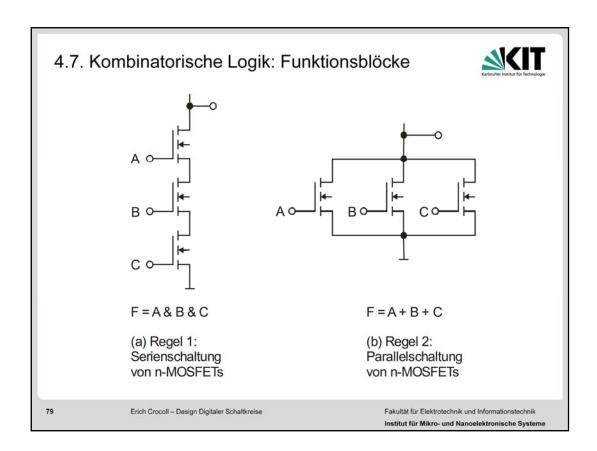

Zur Realisierung der Logikfunktion kann man die nMOS-Tr. Entweder in Reihe (-> NAND) oder parallel (-> NOR) schalten.

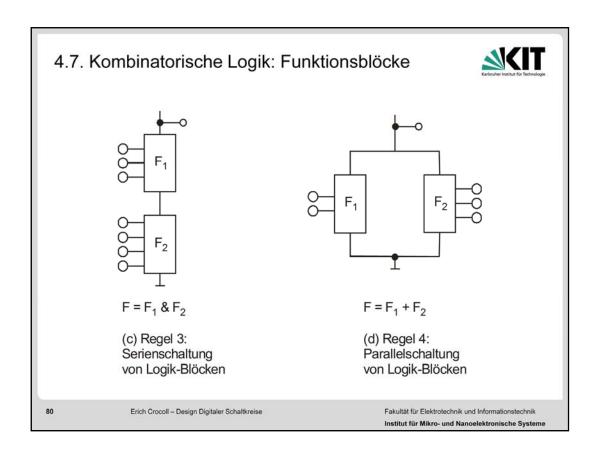

Die nächsten Regeln sagen, dass wir diese nMOS-Funktionsblöcke entweder in Reihe oder parallel schalten können.

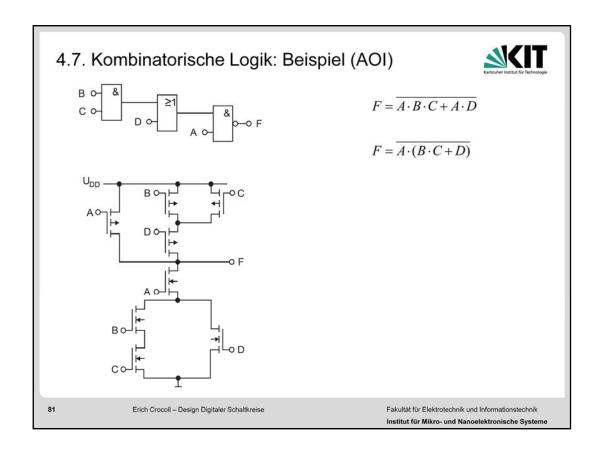

Daraus lässt sich dann eine so genannte AND-OR-Invert –Funktion zusammenbauen. Hier ist eine der möglichen Schaltungsvarianten gezeigt.

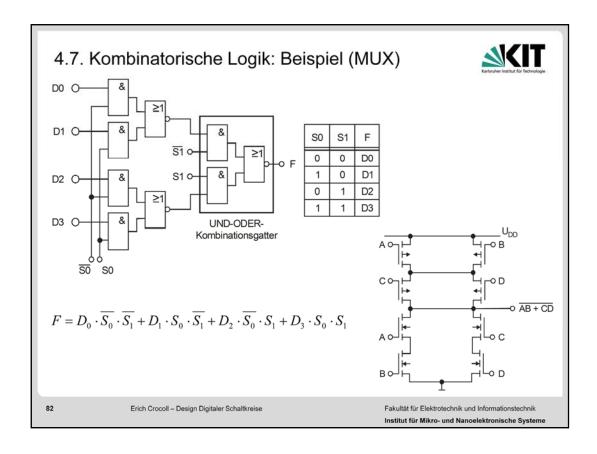

Ein weiteres Beispiel für kombinatorische Logik ist der Schaltungsaufbau eines digitalen Multiplexers.

Über 2 Auswahlleitungen wir einer von vier Eingängen ausgewählt und an den Ausgang weitergeleitet.

Die Realisierung des AND-OR Gatters ist rechts unten zu sehen.

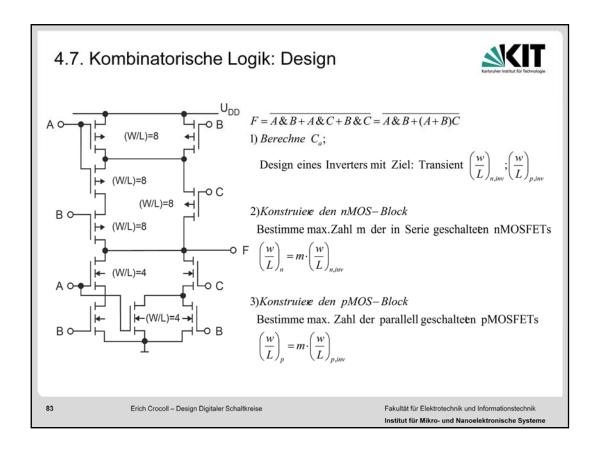

Auch für Logikzellen, die mit kombinatorischer Logik aufgebaut sind, müssen bestimmte Regel beim Design beachtet werden. Hier ein Beispiel

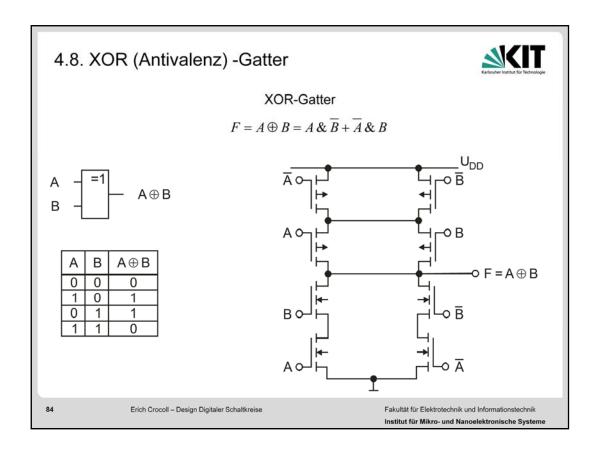

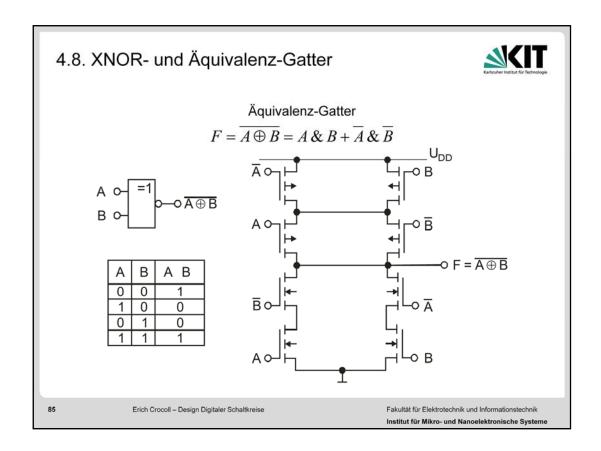

Mithilfe von AND-OR Gattern werden auch die Antivalenzschaltung (diese Folie) und die Äquivalenzschaltung (nächste Folie) aufgebaut.

Wie man aber erkennen kann, werden zusätzlich noch 2 Inverter benötigt, um die invertierten Signale zu generieren.

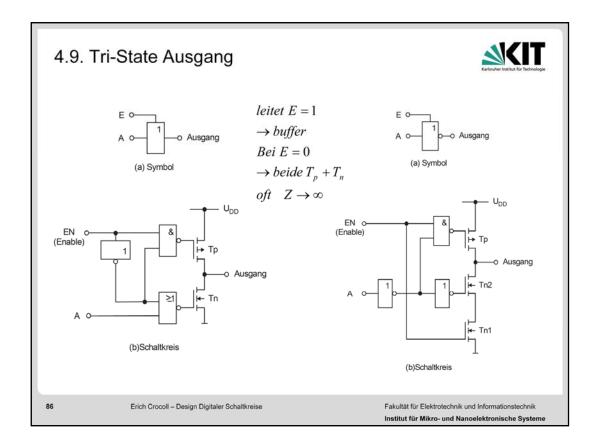

Tri-State Schaltungen werden oft als Ausgangsstufen für Bussysteme eingesetzt.

Neben den beiden logischen Ausgangs-Zuständen H und L kann über den Enable-Eingang ein dritter Zustand: "hochohmig" eingestellt werden.

Es gibt eine Reihe von unterschiedlichen Auslegungen für eine solche Stufe. Hier sind 2 davon gezeigt.

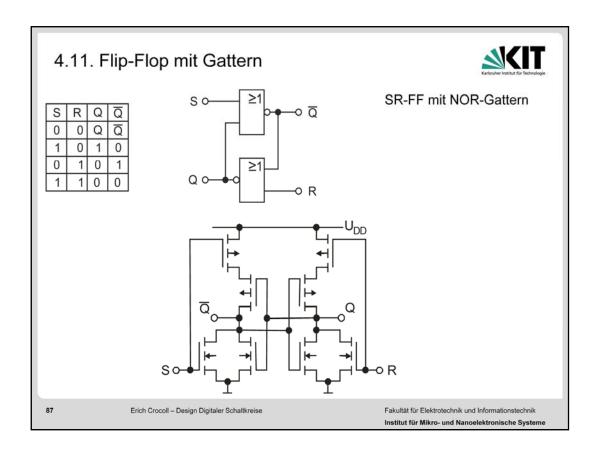

Weitere Beispiele für digitale Standardzellen sind verschiedene Flipflops aus Gattern. Hier ein RS-FF, das mit zwei NOR-Gattern aufgebaut ist.

Die Problematik bei dieser Art von FF-Schaltungen ist, dass für bestimmte Eingangszustände (hier: 1,1) die Ausgangssignale nicht den logischen Deklarationen entsprechen.

Deshalb darf diese Eingangskombination nicht angelegt werden!

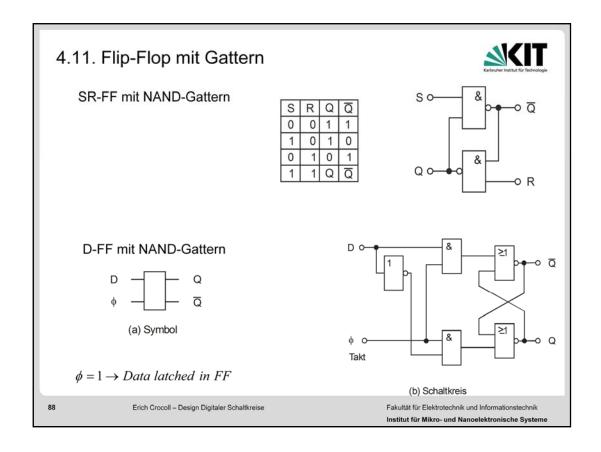

Ein RS-FF, das mit NAND-Gattern aufgebaut ist, unterliegt den gleichen Einschränkungen wie das auf der vorangegangenen Folie.

Erst zusätzliche Logikschaltungen an den Eingängen verhindern diese Restriktionen. Das Einfachste diese Flipflops ist das hier gezeigte D-FF.

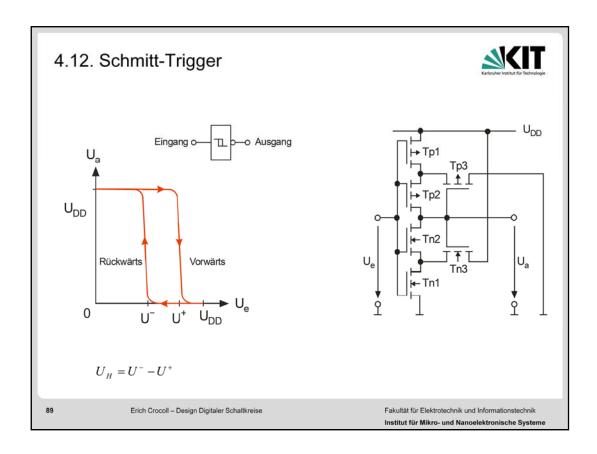

Müssen Signale "konditioniert" werden, bieten sich Schaltungen, wie der Schmitt-Trigger an

Ein Schmitt-Trigger hat eine Hysterese, d.h. die Schaltpunkte sind nicht wie bei den einfachen Gattern sowohl beim Übergang von H->L wie auch beim Übergang von L->H an der gleichen Stelle der Übertagungsfunktion.

Der Vorteil des Schmitt-Triggers ist es, das langsame oder mit Störungen behaftete Signale in einwandfreie logische Pegel mit kurzen Anstiegs- und Abfallzeiten umgewandelt werden.

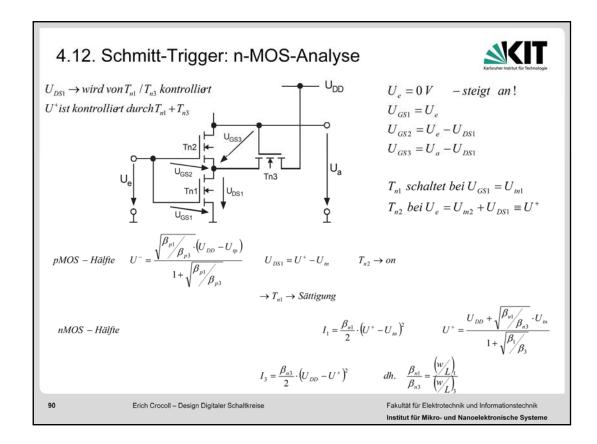

Zur Einstellung der Schaltpegel und der Hysterese muss eine Analyse des Schaltungsdesigns durchgeführt werden.

Dazu werden die beiden Hälften der Schaltung getrennt voneinander betrachtet.

## 4.12. Schmitt-Trigger: Gesamtdesign

Symmetrischer Schmitt - Trigger

$$U^{+} = \frac{1}{2} \cdot U_{DD} + \Delta U$$

$$U^{-} = \frac{1}{2} \cdot U_{DD} - \Delta U$$

$$U_{H} = 2 \cdot (\Delta U)$$

$$\begin{aligned} & \textit{mit } \beta_{\textit{rel}} = \frac{\beta_{\textit{n}1}}{\beta_{\textit{n}3}} = \frac{\beta_{\textit{p}1}}{\beta_{\textit{p}3}} & \textit{and} & U_{\textit{tn}0} = \left| U_{\textit{tp}0} \right| = U_{\textit{t}} \\ & \Delta U = \frac{U_{\textit{DD}} \cdot \left( 1 - \sqrt{\beta_{\textit{rel}}} \right) + 2 \cdot \sqrt{\beta_{\textit{rel}}} \cdot U_{\textit{t}}}{2 \cdot \left( 1 + \sqrt{\beta_{\textit{rel}}} \right)} \end{aligned}$$

$$\rightarrow \sqrt{\beta_{rel}} = \frac{U_{DD} - 2 \cdot \Delta U}{U_{DD} + 2 \cdot \Delta U - 2 \cdot U_{t}}$$

91 Erich Crocoll – Design Digitaler Schaltkreise

Fakultät für Elektrotechnik und Informationstechnik Institut für Mikro- und Nanoelektronische System

Für ein symmetrisches Design lässt sich die Hysterese mit den gezeigten Formeln gut abschätzen.